Vol. 39, No. 11 Nov. 2018

doi: 10.12068/j. issn. 1005 - 3026. 2018. 11. 002

# 改进型 DSC 的并网锁相环直流偏移消除方法

回楠木1,王大志1,李云路2

(1. 东北大学 信息科学与工程学院, 辽宁 沈阳 110819; 2. 沈阳工业大学 电气工程学院, 辽宁 沈阳 110870)

摘 要:针对在 SRF - PLL 的控制内环中使用延迟信号消除(DSC)算子,放缓了动态行为问题,提出了一种用于电网同步的三相 PLL 中的快速直流偏移抑制方法.通过使用改进型 DSC 运算器(MDSC)方法,改进了传统的基于 DSC 的 PLL 的动态性能.该方法能够有效地克服系统带宽给直流偏移消除带来的影响,并使系统响应速度得到提升.另外基于 MDSC 的 PLL 在相位跳变和频率阶跃变化的调整时间也很小.所提方法的有效性通过仿真实验结果得到证实.

关 键 词:直流偏移;同步参考坐标;锁相环;延迟信号消除;相位估计

中图分类号: TM 76 文献标志码: A 文章编号: 1005-3026(2018)11-1526-06

## DC-Offset Elimination Method for Grid-Connected Phase-Locked Loop by Modified DSC

HUI Nan-mu<sup>1</sup>, WANG Da-zhi<sup>1</sup>, LI Yun-lu<sup>2</sup>

(1. School of Information Science & Engineering, Northeastern University, Shenyang 110819, China; 2. School of Electrical Engineering, Shenyang University of Technology, Shenyang 110870, China. Corresponding author: HUI Nan-mu, E-mail; huinanmu@126.com)

**Abstract:** The use of delay signal cancellation (DSC) operator in the control inner loop of SRF-PLL slows down the dynamic behavior. A fast DC-offset rejection method for three-phase PLL of grid synchronization is proposed, which improves the dynamic performance of traditional DSC-based PLL by using the modified DSC operator. This method can effectively overcome the influence of the system bandwidth on the DC-offset elimination and improve the response speed of the system. In addition, the adjustment time of the phase jump and frequency step change based on the MDSC-based PLL is also very small. The effectiveness of the proposed method is confirmed through simulation and experiment results.

**Key words:** DC-offset; synchronous reference flame; phase-locked loop; signal delay cancellation; phase estimation

在理想电网条件下的三相并网应用中,同步参考坐标系锁相环(SRF-PLL)由于其结构简单和高性能成为最普遍的同步技术,广泛用于电力转换器与电网的同步<sup>[1-3]</sup>.但由于电网故障、数字信号处理器中的 A/D 转换、地磁现象、半波整流、电流互感器饱和以及分布式发电系统的直流注入等原因,PLL 输入电压中产生直流偏移<sup>[4-8]</sup>,这将导致由 PLL 估计的相位、频率和振幅中产生基波频率振荡误差以及单位矢量偏移误差.

为了解决 PLL 中直流偏移问题, 文献[5-6]

在 PLL 输入之前使用带通滤波器(BPF)的方法,BPF能有效地阻止直流偏移,但是它会降低 PLL 动态响应,并在频率漂移的情况下导致 PLL 输入的相移. 文献[7]在 PLL 输入端使用了高通滤波器,在这种方法中电网电压首先采用低通滤波器(LPF)来估算直流偏移量,然后用电网电压减去LPF的输出信号用以消除直流偏移. 由于受到LPF阶次和截止频率的影响,该方法会降低 PLL的谐波滤波能力并在其输出端引起相位误差. 文献[8]介绍了5种直流偏移抑制方法的详细研

收稿日期: 2017-07-31

基金项目: 国家自然科学基金重点资助项目(61433004); 国家重点研发计划项目(2017YFB130055).

作者简介:回楠木(1982-),男,辽宁鞍山人,东北大学博士研究生;王大志(1963-),男,辽宁锦州人,东北大学教授,博士生

导师.

究,包括使用 dq 坐标系延时信号消除(dqDSC) 算子和陷波滤波器(NF)消除 PLL 控制内环的直 流偏移,以及使用 αβ 坐标系延时信号消除  $(\alpha\beta DSC)$ 算子,复系数滤波器(CCF)和交叉反馈 网络(CFN)消除 PLL 输入之前的直流偏移.

综上所述,为了实现良好的动态性能且不降 低直流偏移抑制能力,本文提出了一种基于改进 的 DSC 运算器 (MDSC) 方法, 并将其应用于 SRF - PLL 中. 在 50 Hz 电力系统中, MDSC 具有 更短的时间延迟、另外基于 MDSC 的 PLL 在相位 跳变和频率阶跃变化所需的调整时间也很小. 最 后通过仿真和实验验证了方法的有效性.

## 混入直流偏移时 SRF - PLL 的性 能分析

假设锁相环的三相输入电压为

$$v_{a}(t) = V\cos(\omega_{0}t + \varphi) + v_{a,dc}, v_{b}(t) = V\cos(\omega_{0}t + \varphi - 2\pi/3) + v_{b,dc}, v_{c}(t) = V\cos(\omega_{0}t + \varphi + 2\pi/3) + v_{c,dc}.$$

(1)

$$v_{d}(t) = V + \frac{2}{3} \left[ v_{a,dc} \cos(-\theta) + v_{b,dc} \cos(-\theta + \frac{2}{3}\pi) + v_{c,dc} \cos(-\theta - \frac{2}{3}\pi) \right],$$

$$v_{q}(t) = \frac{2}{3} \left[ v_{a,dc} \sin(-\theta) + v_{b,dc} \sin(-\theta + \frac{2}{3}\pi) + v_{c,dc} \sin(-\theta - \frac{2}{3}\pi) \right].$$

(4), 当输入电压直流偏移分量满足

$$daDSC(s) - \frac{\bar{v}(s)}{2} - \frac{1}{2}(1 + e^{-\frac{7}{n}s})$$

分析式(4),当输入电压直流偏移分量满足  $v_{a,dc} = v_{b,dc} = v_{c,dc}$ 时,直流偏移对同步信号提取的 影响可忽略不计[9]. 而当该条件不满足时,由于 输入电压直流偏移在 dq 坐标系下表现为 - 50 Hz 对应的电压成分,因此,SRF-PLL 内环路的直流 偏移抑制方法主要就是消除 - 50 Hz 的电压 分量.

## 基于 MDSC 直流偏移消除方法的 并网锁相环

#### 2.1 基于 DSC 的滤波方法

基于 DSC 的滤波方法是一种被广泛研究的 方法. 传统的 DSC 滤波器通常被设置在 αβ 坐标 系下,也可以在 dq 坐标系下使用.

在 dqDSC 的应用中, dq 坐标系下的电压信 号可被定义为

$$\bar{v}(t) = \frac{1}{2} [v(t) + v(t - T/n)].$$

(5)

其中: $\bar{v}(t)$  是 dqDSC 算子的输出信号;T 是电网 电压额定周期;n 是延迟系数.

dqDSC 的传递函数为

式中:V 为基波电压幅值; $\omega_0$  为电网基波角频率;  $\varphi$  为 a 相电压相角;  $v_{a,dc}$ ,  $v_{b,dc}$ ,  $v_{c,dc}$  分别表示输入 电压在 a,b,c 三相中的直流偏移分量. 利用 Clark 变换式(1),可以得到  $\alpha\beta$  轴电压分量:

$$v_{\alpha}(t) = V\cos\theta + \frac{2}{3}(v_{a,dc} - \frac{1}{2}v_{b,dc} - \frac{1}{2}v_{c,dc}),$$

$$v_{\beta}(t) = V\sin\theta + \frac{\sqrt{3}}{3}(v_{b,dc} - v_{c,dc}).$$

(2)

对式(2)利用 Park 变换可以得到 dq 轴电压分量:

$$\begin{split} v_{d}(t) &= V \text{cos}(\theta - \hat{\theta}) + \frac{2}{3} \left[ v_{a,\text{dc}} \text{cos}(-\hat{\theta}) + \\ v_{b,\text{dc}} \text{cos}(-\hat{\theta} + \frac{2}{3}\pi) + v_{c,\text{dc}} \text{cos}(-\hat{\theta} - \frac{2}{3}\pi) \right], \\ v_{q}(t) &= V \text{sin}(\theta - \hat{\theta}) + \frac{2}{3} \left[ v_{a,\text{dc}} \text{sin}(-\hat{\theta}) + \\ v_{b,\text{dc}} \text{sin}(-\hat{\theta} + \frac{2}{3}\pi) + v_{c,\text{dc}} \text{sin}(-\hat{\theta} - \frac{2}{3}\pi) \right]. \end{split}$$

假定 $\theta$ 为a相电压实际相位角, $\hat{\theta}$ 为锁相环 PLL 输出的 a 相电压相位角. 考虑到稳态情况下 有  $\theta$ ≈ $\hat{\theta}$ ,此时式(3)可以简化为

$$-\theta + \frac{2}{3}\pi\right) + v_{c,dc}\cos\left(-\theta - \frac{2}{3}\pi\right), \left\{ \frac{2}{3}\pi\right) + v_{c,dc}\sin\left(-\theta - \frac{2}{3}\pi\right). \right\} \tag{4}$$

$$dq DSC_n(s) = \frac{\bar{v}(s)}{v(s)} = \frac{1}{2} (1 + e^{-\frac{T}{n}s}) .$$

(6)

将  $s = j\omega$  代入到  $dqDSC_n(s)$  中,可以得到

$$dq DSC_n(j\omega) = \left| \cos \left( \frac{\omega T}{2n} - \frac{\pi}{n} \right) \right| \angle - \left( \frac{\omega T}{2n} - \frac{\pi}{n} \right).$$

(7)

显然, dqDSC, 算子的幅值和时间延迟取决 于延迟系数 n. 由于  $\omega = h\omega_f$  和  $\omega_f T = 2\pi$ ,式(7)可 以用谐波阶次 h 来表达:

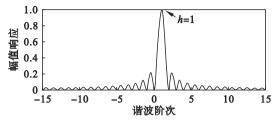

由式(8)可以看出,通过设置不同n值的  $dqDSC_n$  可以消除 dq 坐标下不同阶次的谐波组 并保持直流分量不变. 例如,当 $|dqDSC_2(h)|=0$ 时说明 dq 坐标下  $h = \pm 1, \pm 3, \pm 5, \cdots$ (即 abc 坐 标系下  $h = 0, \pm 2, \pm 4, \pm 6, \cdots$ ) 次谐波被消除, 这意味着 dqDSC2 可以消除电网电压中的所有偶 次谐波.

通过串联多个不同n值的dqDSC 算子可以

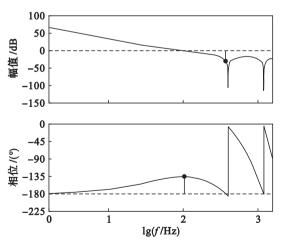

消除任何指定次谐波. 为了在 dq 坐标系下滤除全部谐波干扰,可分别选择 dqDSC<sub>2</sub>, dqDSC<sub>4</sub>, dqDSC<sub>8</sub>, dqDSC<sub>16</sub>, dqDSC<sub>32</sub>来进行串联组成 dqDSC<sub>2,4,8,16,32</sub>. dqDSC<sub>2,4,8,16,32</sub>在 abc 坐标下的幅 频特性如图 1 所示.

图 1 dqDSC<sub>2,4,8,16,32</sub> (s) 的幅频特性 Fig. 1 Magnitude frequency response of the dqDSC<sub>2,4,8,16,32</sub> (s)

然而 dqDSC<sub>2,4,8,16,32</sub>消除所有次谐波是以增加系统延迟时间和计算量为代价的. 由 dqDSC<sub>2,4,8,16,32</sub>算子引入的系统延迟时间  $T_d = T/2 + T/4 + \cdots + T/32 \approx 0.97T$ . 这 0.97 个电网周期的延迟会降低 PLL 的动态性能<sup>[10]</sup>.

### 2. 2 基于 MDSC 直流偏移消除方法的并网锁相 环

传统的 DSC 在 s 域的传递函数为

$$DSC_{n}(s) = \frac{1 + e^{j2\pi/n - (T/n)s}}{2}.$$

(9)

其中,n 是传统 DSC 中唯一的可调参数.

由文献[8]可知,dqDSC<sub>2</sub>可以消除 dq 坐标系下 – 50 Hz 的电压分量,因此采用 dqDSC<sub>2</sub> 滤波单元进行直流偏移消除是一种有效消除 PLL 直流偏移的方法. 但由于 dqDSC<sub>2</sub> 引入的系统延迟时间为 T/2,使得系统的响应速度明显降低. 如果可以减小 dqDSC 的延迟时间,则可以有效降低直流偏移消除过程给系统引入的延迟.

通过对传统 DSC 进行一些修改,可以得到改进型 DSC(MDSC):

MDSC(s) =

$$\frac{1 + e^{j2\pi/n_s - (T/n)s}}{2}$$

. (10)

与传统的 DSC 不同, MDSC 有 n,  $n_s$  两个可以调整的参数,用以设计达到需求的频率特性. 其中, $n_s$  的作用相当于把传统的 DSC 的频率特性在频谱上进行平移.

这里设置参数  $n_s = -16/9$ , n = 16,则对应的 MDSC 所引入的延迟时间为 T/16 (0.001 25 s). 因此 MDSC 的幅频特性可以表示为

$$|\operatorname{MDSC}(j\omega)|_{n_{s_{n}=16}^{n}=16^{9}}| = \frac{1}{2} + \frac{1}{2} \left( -\frac{\sqrt{2}}{2} + j\frac{\sqrt{2}}{2} \right) \left( \cos\frac{0.02}{16}\omega - j\sin\frac{0.02}{16}\omega \right).$$

MDSC 的相频特性可以表示为

$$\angle MDSC(j\omega)^{n_s = -16/9} =$$

$$\tan^{-1}\left(\frac{(\sqrt{2}/2)(\sin(0.02/16)\omega + \cos(0.02/16)\omega)}{1-(\sqrt{2}/2)(\sin(0.02/16)\omega + \cos(0.02/16)\omega)}\right).$$

(12)

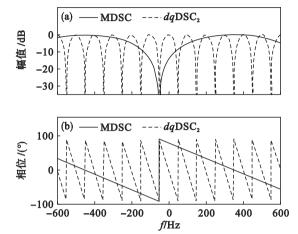

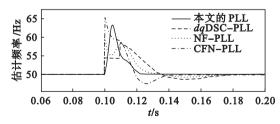

根据式(11),式(12)画出 MDSC 的波特图, 如图 2 所示.

图 2 用于滤除直流分量的 MDSC 和 dqDSC $_2$  波特图 Fig. 2 Bode diagram of MDSC and dqDSC $_2$  for removing DC-offset

(a)—幅值; (b)—相位.

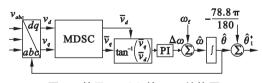

从图中可以看出,当  $n_s = -16/9$ , n = 16 时, MDSC 能够完全消除 PLL 输入端直流分量在 dq 坐标系下的 – 50 Hz 成分. 通过图 2 也可以看出, 经过 MDSC 后的基波正序分量(0 Hz 成分) 的幅值有所衰减,相位超前了 78.8°. 这些基波正序分量幅值和相位上发生的变化会在 SRF – PLL 的输出侧得到补偿. 将 MDSC 结合到传统的 SRF – PLL 的内环. 其结构图如图 3 所示.

图 3 基于 MDSC 的 PLL 结构图

Fig. 3 Block diagram of proposed MDSC-based PLL

由于所提出的基于 MDSC 的 PLL 采用了反正切运算, MDSC 对于基波正序分量的衰减作用不会对相位估计和频率估计造成影响. MDSC 造成的 78.8°相位超前为 0 Hz 成分的相位超前, 因此可以通过在输出端直接进行补偿来修正相位估计值.

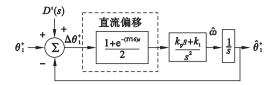

对所提出的 PLL 进行数学建模,其数学模型 如图 4 所示.

图 4 MDSC – PLL 的数学模型 Fig. 4 Mathmatical model of MDSC-PLL

其对应的开环传递函数为

Gol(s) =

$$\frac{\hat{\theta}_1^+}{\Delta \theta_1^+} = \frac{1 + e^{-(T/16)s}}{2} \times \frac{k_p s + k_i}{s^2}$$

. (13)

由于式(13)中包含延迟环节,这会造成分析和设计 PLL 的过程复杂化. 本文采用一阶 Pade 近似的方法将 MDSC 的延迟环节进行如下等效:

$$e^{-(T/16)s} \approx \frac{1 - sT/32}{1 + sT/32}$$

(14)

则 MDSC - PLL 的开环传递函数可以表示为

$$Gol(s) \approx \frac{1}{1 + s(T/32)} \times \frac{k_p s + k_i}{s^2}$$

. (15)

应用文献[8]中的对称最优设计方法对式 (15)所代表的系统进行 PI 控制器参数设计,可以 得到 PI 控制器的两个参数为

$k_{\rm p}=1/(b(T/32))$ , $k_{\rm i}=1/(b^3(T/32)^2)$ . (16) 其中,b 是影响系统相位裕度的参数,通常选取  $b=1+\sqrt{2}$ ,则对应的控制器参数  $k_{\rm p}$  和  $k_{\rm i}$  分别为 662 和 182 012. 系统的开环传递函数波特图如图 5 所示. 其相位裕度为 43. 8°,对应频率为 105 Hz. 其幅值裕度为 29. 5 dB,对应频率为 370 Hz.

图 5 MDSC - PLL 开环波特图 Fig. 5 Open-loop Bode diagram of MDSC-PLL

可以发现,由于 MDSC - PLL 采用了频率非对称的 MDSC 作为直流偏移消除方法,且 MDSC 的延迟时间相比 dqDSC 明显减小,系统的带宽相比 dqDSC 的带宽大幅度增加,因此其系统响应速度也会得到提升.

### 3 仿真与实验结果及分析

为了验证本文算法在三相电压混入直流偏移 分量情况下,电压发生相位跳变、频率跳变时,所 提出的 PLL 的相位估计、频率估计性能,本文对 基于所提出的直流偏移消除方法的锁相环进行仿 真及实验验证.

#### 3.1 仿真及结果分析

仿真实验在 MATLAB/Simulink 的软件环境下进行.整个仿真实验的采样频率设置为10 kHz.设定被测三相电压额定频率为 50 Hz,幅值归一化为1 p. u.. 在对仿真模型进行离散化的过程中,采用 Adams – Bashforth 方法保证系统离散后的精度,同时防止仿真出现代数环. 所采用的连续域与离散域的积分环节对应关系:

$$\frac{1}{s} \Leftrightarrow \frac{T_s}{12} \frac{23z^{-1} - 16z^{-2} + 5z^{-3}}{1 - z^{-1}}.$$

(17)

为了进行对比仿真,多种应用其他直流偏移消除方法的 PLL 被同时进行对比仿真. 由于本文提出的 PLL 所采用的直流消除方法是基于MDSC 的方法, dqDSC - PLL 将用于对比仿真中<sup>[8]</sup>. 此外,文献[8]中的 NF - PLL 和 CFN - PLL 也参与到对比仿真实验中.

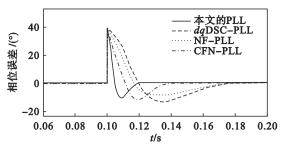

#### 3.1.1 相位跳变仿真

将三相电压中混入直流偏移量,a,b,c 相分别混入直流偏移量 -0.1 p. u. ,0.05 p. u. ,0.05

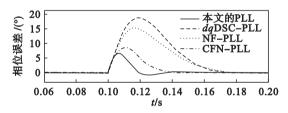

图 6 电网电压 + 40°相位阶跃跳变下电网频率估计 Fig. 6 Estimated frequency waveform with grid voltage under + 40° phase jump

从图中可以发现,本文提出的 PLL 的调节时间最短,在1个电网周期左右;CFN – PLL 的动态调节时间次之;dqDSC – PLL 和 NF – PLL 的动态调节时间超过3个电网周期,不符合电网设备并网调节时间的标准.

图 7 电网电压 +40°相位阶跃跳变下相位估计误差 Fig. 7 Phase error waveform with grid voltage under +40° phase jump

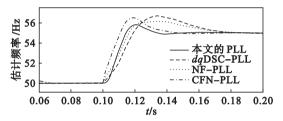

#### 3.1.2 频率跳变仿真

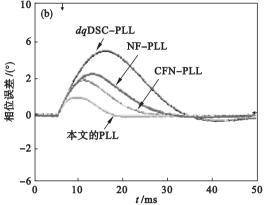

图 8 为电网电压三相电压中混入直流偏移后在 0.1 s 发生了 +5 Hz 的频率跳变时 4 种 PLL 的电网频率估计值的波形图. 图 9 为 4 种 PLL 的相位估计误差波形图.

图 8 电网电压 +5 Hz 频率跳变下电网频率估计 Fig. 8 Estimated frequency waveform with grid voltage under +5 Hz frequency step change

图 9 电网电压 +5 Hz 频率跳变下相位估计误差 Fig. 9 Phase error waveform with grid voltage under +5 Hz frequency step change

从图 8 中可以看出,本文所提出的 PLL 在经过大约 1.5 个电网周期后实现了对电网频率的准确估计,与其他 3 种方法相比耗时最少. 从图 9 中可以看出,当电网发生频率跳变时,所提出的 PLL 能够在 1.5 个电网周期的时间内恢复对电网基波正序分量的相位跟踪.

#### 3.2 实验及结果分析

实验基于 TMS320F28335 的 DSP 展开,使用 该型号 DSP 制作了任意波形发生器并产生三相 电压信号,整个实验的采样频率为 10 kHz. 设定 被测三相电压额定频率为 50 Hz,幅值归一化为 1 p. u..

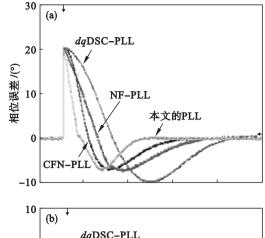

图 10 为电网电压发生 +40°相位阶跃跳变和

发生 +5 Hz 频率跳变时,参与对比的 4 种 PLL 的相位估计误差曲线.

图 10 电网电压不同跳变下相位估计误差实验波形 Fig. 10 Phase error experimental results with grid voltage undergoes different step changes

- (a)—电网电压 +40°相位阶跃跳变下相位估计误差;

- (b)—电网电压 +5 Hz 频率跳变下相位估计误差.

实验结果与仿真实验结果基本保持一致,进一步验证了本文所提出的 PLL 及其直流偏移消除方法能够具有较快的响应速度,同时既达到了滤波的效果,又保持了系统的带宽.

### 4 结 论

- 1) 提出了一种基于 MDSC 的直流偏移消除 方法,并将该方法结合到传统的 SRF PLL 中.

- 2) 该方法能够有效地克服系统带宽给直流 偏移消除带来的影响,并使系统响应速度得到 提升.

- 3) 通过三相电网混入直流偏移情况下的仿 真及实验,验证了本文方法的有效性.

#### 参考文献:

[1] Golestan S, Guerrero J, Vidal A, et al. Small-signal modeling, stability analysis and design optimization of single-phase delay-based PLLs [J]. *IEEE Transactions on Power Electronics*, 2016, 31 (5):3517 – 3527.

- [2] Zhang G, Wang G, Xu D G, et al. ADALINE network based PLL for position sensorless interior permanent magnet synchronous motor drives [J]. *IEEE Transactions on Power Electronics*, 2016, 31(2):1450-1460.

- [3] Bifaretti S, Lidozzi A, Solero L, et al. Anti-islanding detector based on a robust PLL [J]. *IEEE Transactions on Industry Applications*, 2015, 51(1):398-405.

- [4] Ghartemani M K, Khajehoddin S, Jain P, et al. Addressing DC component in PLL and notch filter algorithms [J]. *IEEE Transactions on Power Electronics*, 2012, 27(7):78 86.

- [5] Ghartemani M K, Mojiri M, Safaee A, et al. A new phase-locked loop system for three-phase applications [J]. *IEEE Transactions on Power Electronics*, 2013, 28 (3): 1208 1218.

- [6] Luna B E O B, Jacobina C B, Oliveira A C. A new PLL structure for single-phase grid-connected systems [C]// IECON 2011: The 37th Annual Conference of the IEEE Industrial Electronics Society. Melbourne, 2011:1081 1084.

- [7] Dong D, Boroyevich D, Mattavelli P, et al. A high performance single-phase phase-locked-loop with fast line-

- voltage amplitude tracking [C]//2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). Fort Worth, 2011:1622 1628.

- [8] Golestan S, Guerrero J M, Gharehpetian G. Five approaches to deal with problem of DC offset in phase-locked loop algorithms; design considerations and performance evaluations [J]. IEEE Transactions on Power Electronics, 2016, 31 (1):648-660.

- [9] 杜雄,刘延东,孙鹏菊,等. 消除直流分量影响的并网变流器同步参考坐标系锁相环方法[J]. 电工技术学报,2013,28(12);24-31.

(Du Xiong, Liu Yan-dong, Sun Peng-ju, et al. SRF-PLL method of grid-tied converter to eliminating the effect of DC components [J]. Transactions of China Electrotechnical Society,2013,28(12);24-31.)

- [10] Huang Q, Rajashekara K. An improved delayed signal cancellation PLL for fast grid synchronization under distorted and unbalanced grid condition [J]. *IEEE Transactions on Industry Applications*, 2017, 53(5):4985-4997.

#### (上接第1525页)

- [8] 冯凯, 贺东风, 徐安军, 等. 钢包调度评价方法研究[J]. 东 北大学学报(自然科学版), 2015, 36(12):1728-1732. (Feng Kai, He Dong-feng, Xu An-jun, et al. Research on the evaluation method of ladle scheduling [J]. *Journal of* Northeastern University (Natural Science), 2015, 36(12): 1728-1732.)

- [9] Wang B, Wang B, Mu Y Q, et al. Optimization and control of ladle peration for special steel plants [J]. Applied Mechanics and Materials, 2014, 602:899 - 902.

- [10] Tan Y, Cheng T E, Ji M. A multi-objective scatter search for

- the ladle scheduling problem [J]. *International Journal of Production Research*, 2014,52(24):7513-7528.

- [11] 周志华. 机器学习[M]. 北京:清华大学出版社,2016:350 359.

(Zhou Zhi-hua. Machine learning [M]. Beijing: Tsinghua

University Press, 2016:350 - 359.)

[12] Chen J F, Hsieh H N, Do Q H. Evaluating teaching performance based on fuzzy AHP and comprehensive evaluation approach [J]. *Applied Soft Computing*, 2015, 28: 100 – 108.